- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT5V49EE902NLGI (IDT, Integrated Device Technology Inc)IC CLOCK GEN PLL 500MHZ 32VFQFPN

IDT5V49EE902

EEPROM PROGRAMMABLE CLOCK GENERATOR

CLOCK SYNTHESIZER

IDT EEPROM PROGRAMMABLE CLOCK GENERATOR

15

IDT5V49EE902

REV P 092412

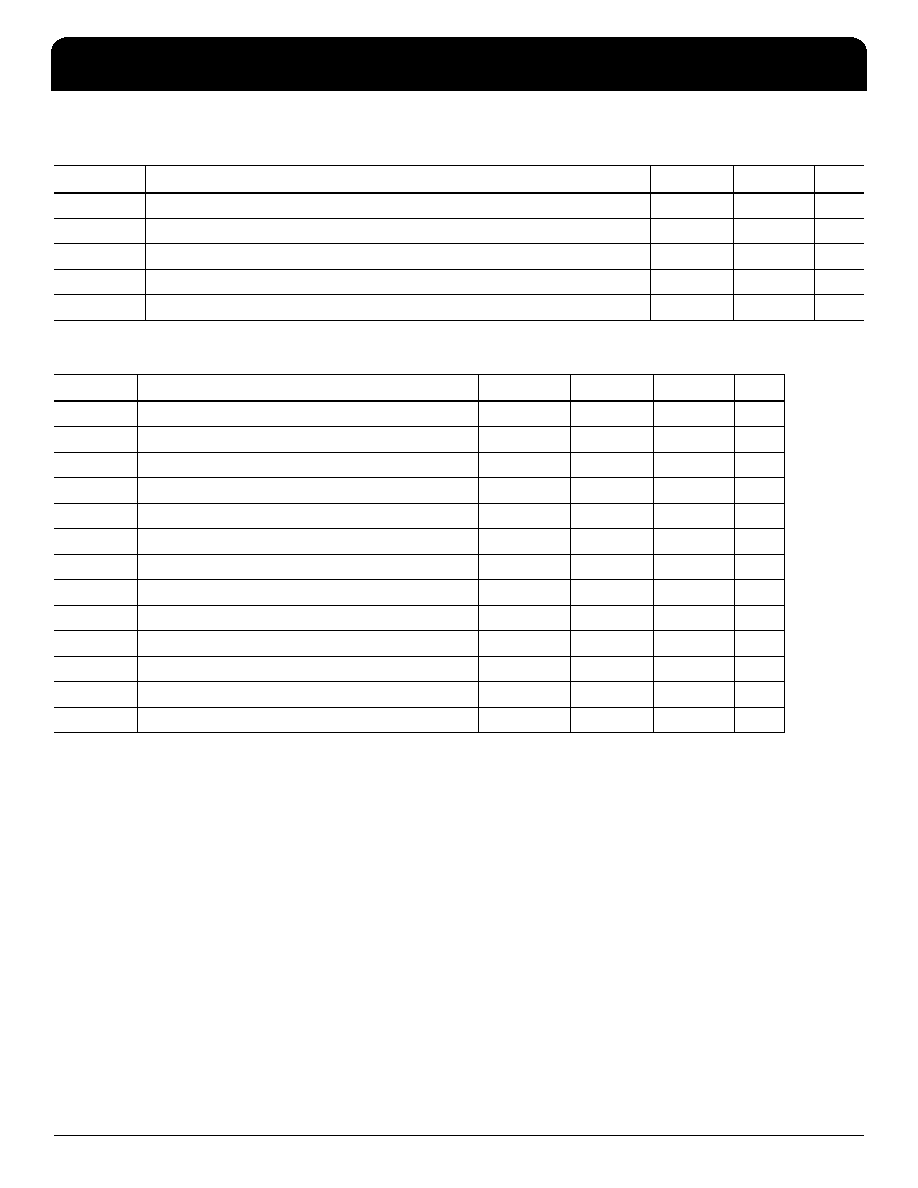

I2C Bus DC Characteristics

I2C Bus AC Characteristics for Standard Mode

Note 1: A device must internally provide a hold time of at least 300 ns for the SDAT signal (referred to the VIH(MIN)

of the SCLK signal) to bridge the undefined region of the falling edge of SCLK.

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VIH

Input HIGH Level

0.7xVDD

V

VIL

Input LOW Level

0.3xVDD

V

VHYS

Hysteresis of Inputs

0.05xVDD

V

IIN

Input Leakage Current

±1.0

A

VOL

Output LOW Voltage

IOL = 3 mA

0.4

V

Symbol

Parameter

Min

Typ

Max

Unit

FSCLK

Serial Clock Frequency (SCL)

0

100

kHz

tBUF

Bus free time between STOP and START

4.7

s

tSU:START Setup Time, START

4.7

s

tHD:START Hold Time, START

4

s

tSU:DATA

Setup Time, data input (SDA)

250

ns

tHD:DATA

Hold Time, data input (SDA) 1

0s

tOVD

Output data valid from clock

3.45

s

CB

Capacitive Load for Each Bus Line

400

pF

tR

Rise Time, data and clock (SDAT, SCLK)

1000

ns

tF

Fall Time, data and clock (SDAT, SCLK)

300

ns

tHIGH

HIGH Time, clock (SCLK)

4

s

tLOW

LOW Time, clock (SCLK)

4.7

s

tSU:STOP

Setup Time, STOP

4

s

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT5V49EE904NLGI8

IC PLL CLK GEN 200MHZ 32VFQFN

IDT821024PPG

IC PCM CODEC QUAD NONPROG 44TQFP

IDT821034DNG

IC PCM CODEC QUAD MPI 52-PQFP

IDT821054PQF

IC PCM CODEC QUAD MPI 64-PQFP

IDT82V3001APVG8

IC PLL WAN W/SGL REF INP 56-SSOP

IDT82V3010PVG

IC PLL WAN 51/E1/OC3 DUAL 56SSOP

IDT82V3011PVG

IC PLL WAN T1/E1/OC3 SGL 56-SSOP

IDT82V3012PVG8

IC PLL WAN T1/E1/OC3 DUAL 56SSOP

相关代理商/技术参数

IDT5V49EE902NLGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 32QFN

IDT5V49EE903NLGI

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR

IDT5V49EE903NLGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 32QFN

IDT5V49EE903PGGI

制造商:Integrated Device Technology Inc 功能描述:IC CLOCK GENERATOR

IDT5V49EE903PGGI8

制造商:Integrated Device Technology Inc 功能描述:IC CLK GEN EEPROM PROGR 28TSSOP

IDT5V49EE904NLGI

功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR

IDT5V49EE904NLGI8

功能描述:IC PLL CLK GEN 200MHZ 32VFQFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:VersaClock™ III 标准包装:1,000 系列:- 类型:时钟/频率合成器,扇出分配 PLL:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 除法器/乘法器:- 电源电压:- 工作温度:- 安装类型:表面贴装 封装/外壳:56-VFQFN 裸露焊盘 供应商设备封装:56-VFQFP-EP(8x8) 包装:带卷 (TR) 其它名称:844S012AKI-01LFT

IDT5V50009DCG

功能描述:IC PC CLOCK 8-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:39 系列:- 类型:* PLL:带旁路 输入:时钟 输出:时钟 电路数:1 比率 - 输入:输出:1:10 差分 - 输入:输出:是/是 频率 - 最大:170MHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:* 封装/外壳:* 供应商设备封装:* 包装:*